DDR4 記憶體即將導入個人電腦平台,簡單看懂改朝換代的意義

JEDEC 於 2012 年間,正式發布下一世代記憶體標準規範 DDR4,相較於現行 DDR3 資料傳輸速率上看 3200Mbps,標準電壓由 DDR3 的 1.5V 調降至 1.2V,意味性能提升之餘還更為省電。Intel 預定年底推出的 X99 平台將會率先支援,在此之前先來簡單搞懂,升級 DDR4 的效益究竟是?

JEDEC 於 2012 年間,正式發布下一世代記憶體標準規範 DDR4,相較於現行 DDR3 資料傳輸速率上看 3200Mbps,標準電壓由 DDR3 的 1.5V 調降至 1.2V,意味性能提升之餘還更為省電。Intel 預定年底推出的 X99 平台將會率先支援,在此之前先來簡單搞懂,升級 DDR4 的效益究竟是?記憶體規格的演進,向來令眾多使用者牙癢癢,因為新世代製品價格必然高出一截。不過除非規範早已不敷應用需求、製造商面臨物理限制,否則 JEDEC(Joint Electron Device Engineering Council ,美國電子工程設計發展聯合協會)還不至於善變的頻繁更改規格,各世代記憶體的生命週期說來還算是頗長。

DDR3 瓶頸是卡在速率實現

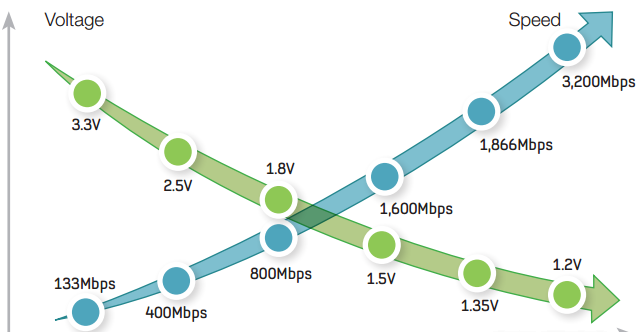

▲ 近代記憶體規範演進歷程示意圖,變化是工作電壓降低、資料傳輸速率提升。

現行 DDR3 規範是於 2007 年頒布,約莫在 2009 年起開始大量導入個人電腦平台應用,典型規格特徵為 DDR3-800 / 800Mbps、1.5V。JEDEC 因應各類電腦系統、行動裝置,對於節能省電與性能的需求,前些年陸續再頒布 DDR3-1866/2133、DDR3L 1.35V 低電壓等規範。

時至今日,DDR3 仍然算是好用,不過已經漸漸無法滿足 HPC(High-performance computing system,高效能計算系統)之類商業應用的需求。資料傳輸速率為其中關鍵,即便你能舉一反三的說,DDR3 不也是能達到如 DDR3-2600 以上速率規格了,沒有非要 DDR4 不可的理由吧?

得留意,那可是藉由 XMP 之類超頻功能而來,既然是超頻那就有相容性問題。其次雖然 JEDEC 規範已經開到 DDR3-2133,晶圓廠是否願意大量投產原生顆粒也是個問題,現實是常見最高規格原生顆粒仍停留在 DDR3-1600。因此那些高時脈模組,都是拿比如 DDR3-1600 之類顆粒超頻而來,代價是得提高工作電壓。左看右看,這招顯然不適用於商用電腦環境,如此便構成改朝換代的合理性。

DDR4 傳輸速率上看 3200Mbps

▲ 此示意圖是以雙通道組合為比較基礎。

依據 JEDEC 當前頒布規範而言,DDR4 起始規格為 DDR4-1600,理論資料傳輸頻寬為 12.8GB/s。其餘規格分別是 DDR4-1866(14.9GB/s)、DDR4-2133(17GB/s)、DDR4-2400(19.2GB/s)、DDR4-2666(21.3GB/s),目前規範定義最高規格是 DDR4-3200,資料傳輸頻寬高達 25.6GB/s。

反觀 DDR3 世代產品,當前常見產品規格是 DDR3-1333(10.6GB/s)、DDR3-1600(12.8GB/s),在零售通路市場很容易購買到原生顆粒模組產品。雖然 JEDEC 已將 DDR3-1866(14.9GB/s)、DDR3-2133(17GB/s)納入規範中,由於需要較先進製程來生產,基於獲利有限且 DDR4 即將到來等因素,晶圓廠投產意願有限而不容易看到。

如同 DDR2 跨入 DDR3 世代那樣,從 DDR3 進化到 DDR4 世代,彼此高、低規格產品同樣會重疊到。不過就現實面而言,當模組廠商生產意願提高,市場上也比較容易購買到實體產品時,通常已經距離首波上市產品一段時日。未來我們實際採購 DDR4 模組時,能買到的基本規格產品也許是 DDR4-1866 甚至 DDR4-2133,升級的動作並不會失去意義。(以 Micron 目前產出的樣品為例,是自 DDR4-2133 起跳)

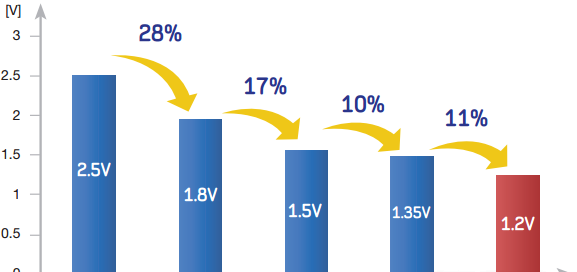

預設工作電壓降低 20%

▲ JEDEC 亦擬定了 DDR4 低電壓規範,可低至 1.05V。

除了資料傳輸速率的提升,DDR4 另一改革重點是基本工作電壓降低,由 DDR3 的 1.5V 調降到 1.2V。規範中亦擬定了低電壓版本,現行 DDR3L 是 1.35V,低電壓版本 DDR4 預估是約為 1.05V。單看這數值頗為無感,其意義是在於解決高時脈耗電量問題,因為電流需求量會伴隨脈提升而拉高,簡單帶入功率公式即可看出效益。

雖然電壓值看起來不過約莫 20% 差距,得留意在現實中,DDR3-1866、1.5V 原生顆粒已經很少見,更遑論原生 DDR3-2133 顆粒。那些超過 DDR3-1866 時脈組態的模組,都是採用 DDR3-1600 甚至 DDR3-1333 顆粒超頻而來,故電壓普遍會拉高到 1.60~1.7V 不等,意味耗電量會隨之拉高更多。基於這些現實面限制因素,不容忽視 DDR4 這看似小小的變化,這可是相當關鍵的轉變。

▲ DDR4 產品普遍將以目前最先進的半導體製程投產,其目標為 2xnm 世代。

DDR3 自 2007 年頒布以來,廠商不盡然是以 4xnm 世代製程投產,最早先可是從 5xnm 這樣一路演進走過來。DDR4 基於新世代產品結構上有些許的不同,而且初期投入量產的毛利比較高,晶圓廠會願意以最新製程技術來生產。新製程有利於改善半導體漏電流現象,能夠降低真實消耗功率,並且讓工作溫度也降低些。

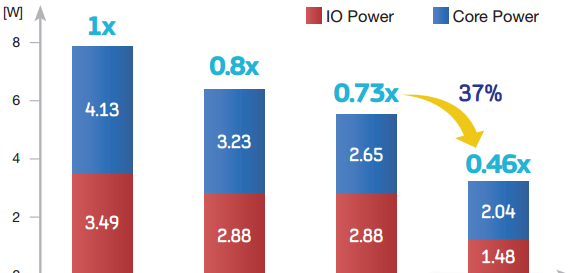

此外,DDR4 架構中新增了 POD(Pseudo Open Drain,偽開放汲極)介面,用以減少 I/O 電源消耗量,據稱讀寫資料理論消耗功率隻有 DDR3 的一半左右。因此從消耗功率角度來看,DDR4 節能性可就不隻電壓值那區區約 2x% 差異而已,實體產品可能會如配圖顯示那般高。

新增 Bank Group 群組設計

▲ 舊世代記憶體規範架構示意圖。

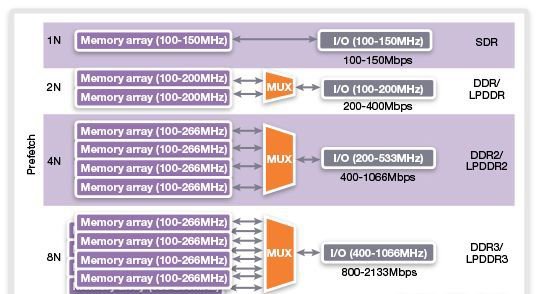

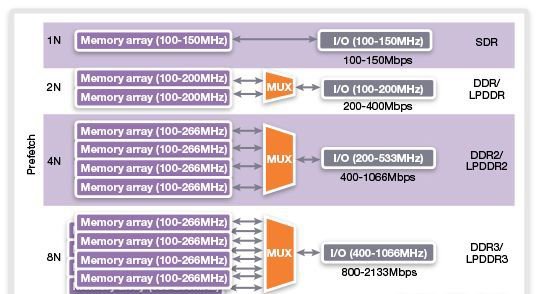

DDR 記憶體核心架構中都具備預取(Prefetch)機制,當前主流 DDR3 模組為 8N 設計,DDR4 沿用了這設計,此外還新增納入 Bank Group 架構設計。預取意味在 1 個時脈週期內,得以傳輸多少資料量給予 I/O Buffer 單元,8N 即代表為 8bit。參考配圖來看預取架構,可以將之想像為記憶體模組內部運作,預取設計數量相似於多通道概念。

DDR4 如能提升至 64N 設計,和時下 64bit 處理器的暫存器(Register)對等匹配,1 個時脈週期就能傳送完 1 筆運算處理資料,那麼理論效率自然會更佳。不過這將導緻線路布局複雜化,從而使得製造成本攀升,因此 JEDEC 維持了 8N 結構設計。

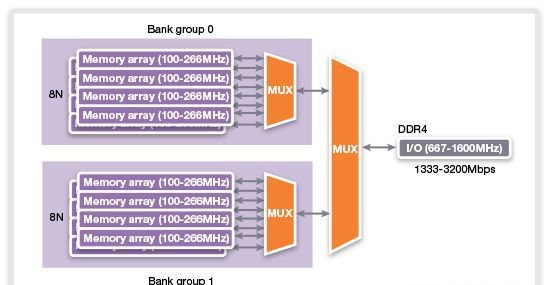

但是為了進一步提高效率(縮短存取延遲),DDR4 新增了 4 個 Bank Group 資料組設計,如下圖所示組成幾個小群組,具備獨立啟動操作讀、寫等動作特性。Bank Group 資料組可套用多工的觀念來想像,這代表 DDR4 在同一時脈工作周期內,至多可以處理 4 筆資料,效率自然是好過於 DDR3。

▲ DDR4 記憶體規範架構示意圖。

預取和記憶體核心時脈有連動關係式,簡單換算法是傳輸速率除以預取數量,可得到真實核心時脈。例如 DDR3-1600 是代表數據速率,基於 DDR3 採用 8N 預取架構,那麼 1600 / 8 即為 200MHz。壓低核心時脈為之重要,考量點不外乎是設計難度、生產良率、物理限制,乃至於總和的生產成本等考量。

因此在這 2 張示意圖中,可發現從 SDRAM 一路至 DDR4,記憶體陣列內的時脈標示,是落在 100~266MHz 之譜。其中 DDR2、DDR3 即便同為 100~266MHz,圖例顯示 I/O 傳輸速率卻是 DDR2-1066 與 DDR3-2133 之別,這正是基於預取架構的因素。

顆粒改採用 8CE 堆疊封裝

▲ DDR4 模組基本容量為 4GB,不久的未來要達到 16GB 相當輕而易舉。

由此可見,DDR4 的變革是利多於弊,而且除了帶來更高資料傳輸速率,其預設基本容量也有所提升。DDR3 記憶體顆粒,標準是採用 4 顆裸晶圓堆疊封裝,DDR4 將堆疊數量增加到 8 顆。意味在桌上型電腦常見雙面配置組合模式下,DDR4 模組須在電路闆上塞入 2 倍數量顆粒,即可提供 2 倍於 DDR3 產品的容量,。

DDR3 模組基本容量為 1GB,目前大量量產的產品之中,單支常見最高容量為 8GB(雙面模組共配置 16 顆顆粒)。雖然亦有 16GB 產品推出,但模組廠商大多走變通模式,在電路闆正反兩面塞入 32 顆顆粒來達成,這並非是常態。而 DDR4 基本容量是設定在 4GB,視晶圓廠顆粒產出狀態而言,未來想採購單支 16GB 模組並非難事,隻要口袋小朋友足夠就可行。

以上簡而言之,DDR4 對使用者而言,初期確實是有投入成本比較高等問題。但是其優勢為資料傳輸速率更高、消耗功率更低,而且得以帶來更高容量單一模組,概觀而言是利多弊少。